AMD下代显卡曝光,至高96CU配置挑战英伟达旗舰

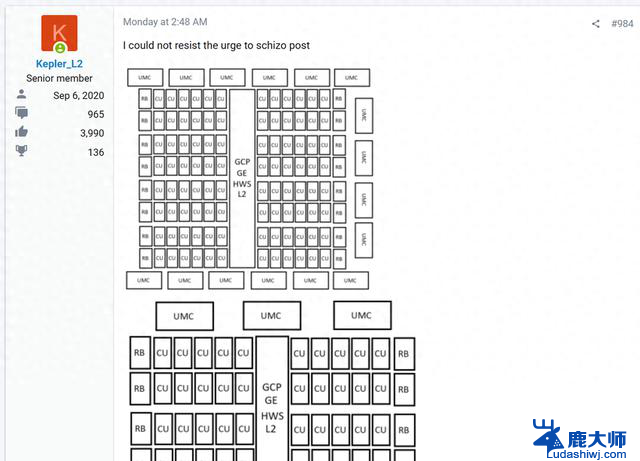

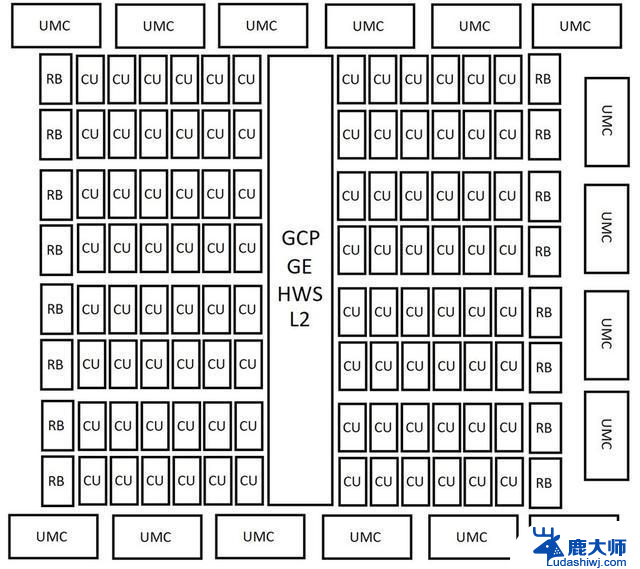

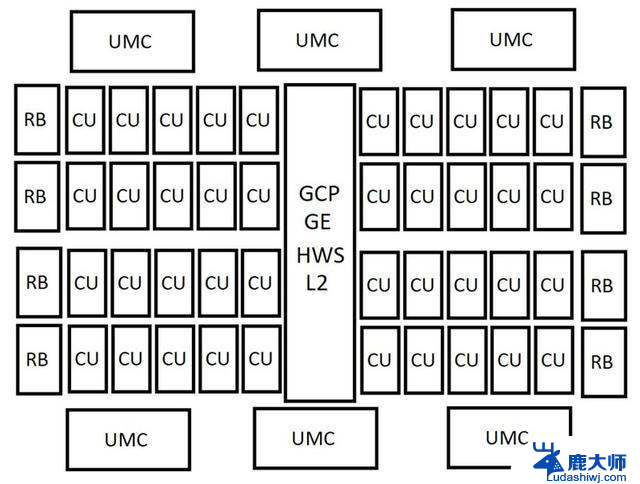

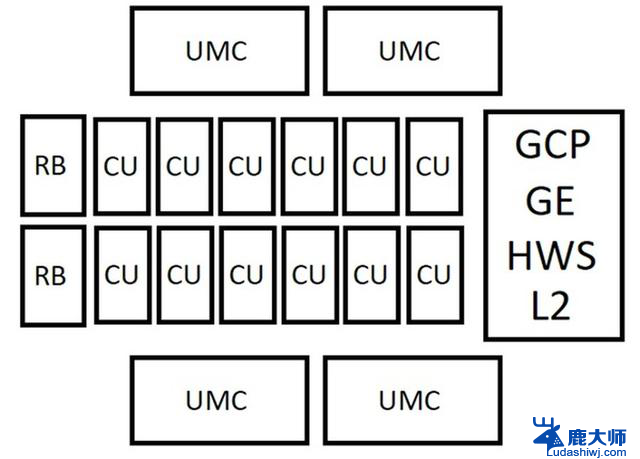

知名爆料人Kepler_L2在AnandTech论坛上发布了这四种核心的设计示意图,具体的配置信息和对应图片如下:

AT0,拥有8个着色器阵列 / 16个着色引擎(每组着色器阵列有2个着色引擎)/ 96个CU(每个着色引擎有6个CU)/ 位宽512-bit(16个32-bit显存控制器)/ Infinity Cache最多为128MB。

AT2,拥有4个着色器阵列 / 8个着色引擎(每组着色器阵列有2个着色引擎)/ 40个CU(每个着色引擎有6个CU)/ 位宽192-bit(6个32-bit显存控制器)/ Infinity Cache预计为48MB。

AT3,拥有2个着色器阵列 / 4个着色引擎(每组着色器阵列有2个着色引擎)/ 24个CU(每个着色引擎有6个CU)/ 位宽128或256-bit(8个16或32-bit显存控制器)/ Infinity Cache可能是32MB。

AT4,拥有1个着色器阵列 / 2个着色引擎(每组着色器阵列有2个着色引擎)/ 12个CU(每个着色引擎有6个CU)/ 位宽64或128-bit(4个16或32-bit显存控制器)/ Infinity Cache可能是16MB。

AMD在最近的Hot Chips 2025上,暗示UDNA架构可能采用模块化的设计,以提供更为灵活的配置方案。而结合上述配置来看,AT3的显存控制器数量甚至比高一级的AT2还要多,结合近日有传闻说AT3和AT4将引入LPDDR6/5X, 取代GDDR作为显存,推测可能与这个改动有关。

AMD下代显卡曝光,至高96CU配置挑战英伟达旗舰相关教程

- AMD数据中心GPU销售预期上调,下代芯片挑战英伟达竞争力

- 约4300元起!英伟达RTX 40 SUPER显卡价格曝光,性能强悍,性价比高!

- 继续狙击英伟达,AMD子弹已上膛丨焦点分析:AMD如何挑战英伟达?

- 英伟达RTX50显卡规格曝光,4090Ti再曝光

- 英伟达RTX 5060 Ti显卡完整规格曝光:16GB显存,180W TDP详细解读

- 谁能挑战英伟达?全球GPU市场霸主的挑战者是谁?

- 英伟达30HX6G显存容量显卡3DMARK最高7000分,鲁大师28万1660,199元购买

- 英伟达,大消息!全新显卡发布,性能再创高峰

- AMD Zen5C、Zen6架构细节曝光:核心数创新高,性能提升明显

- AMD RDNA 5被曝最高96个计算单元,2026显卡大战前瞻

- Windows 快捷键与效率技巧大全(Win10/Win11):提高工作效率的必备技能

- 微软Win11 23H2八月可选更新:修复简中输入和设备管理BUG

- 处理器的主要类别:最常见的CPU类型及其特点

- 英伟达:NVLink Fusion互联授权支持CPU XPU双定制芯片,加速人工智能计算

- AMD台式机独显首次引入LPDDR6/5X,将取代GDDR成为显存标准

- NVIDIA 校招 | 2025 实习生招聘末班车等你上车!优质岗位等你来挑战

热门推荐

微软资讯推荐

- 1 微软Win11 23H2八月可选更新:修复简中输入和设备管理BUG

- 2 AMD台式机独显首次引入LPDDR6/5X,将取代GDDR成为显存标准

- 3 NVIDIA 校招 | 2025 实习生招聘末班车等你上车!优质岗位等你来挑战

- 4 AI进化速递丨英伟达明天公布人形机器人“黑科技”,震撼全球科技界

- 5 AMD RX 9070 XT显卡16针接口熔化问题原因分析及解决方案

- 6 OMEN暗影精灵11重现散热、显卡巅峰实力,年度战争游戏战地6公测!

- 7 AMD主导游戏掌机市场,垄断红利背后的创新停滞:AMD掌机市场垄断优势何在?

- 8 微软不再允许关闭 Microsoft Store 中的应用更新,用户需及时更新应用程序

- 9 提高显卡散热效果的苏州元脑智能申请散热装置控制相关专利

- 10 无需第3方工具,Windows10/11如何永久关闭自动更新?最简易方法揭秘

win10系统推荐

系统教程推荐

- 1 windows10flash插件 如何在Win10自带浏览器中开启Adobe Flash Player插件

- 2 台式机win10怎么调节屏幕亮度 Win10台式电脑如何调整屏幕亮度

- 3 笔记本电脑怎样设置密码开机密码 如何在电脑上设置开机密码

- 4 笔记本键盘不能输入任何东西 笔记本键盘无法输入字

- 5 苹果手机如何共享网络给电脑 苹果手机网络分享到台式机的教程

- 6 钉钉截图快捷键设置 电脑钉钉截图快捷键设置方法

- 7 激活windows7家庭普通版密钥 win7家庭版激活码序列号查询

- 8 wifi有网但是电脑连不上网 电脑连接WIFI无法浏览网页怎么解决

- 9 适配器电脑怎么连 蓝牙适配器连接电脑步骤

- 10 快捷删除是哪个键 删除快捷键ctrl加alt